Numonyx® Flash Memory (P33-65nm)

256-Mbit, 512-Mbit (256M/256M)

Datasheet

Product Features

High performance:

— 95ns initial access time for Easy BGA

— 105ns initial access time for TSOP

— 25ns 16-word asynchronous-page read

mode

— 52MHz (Easy BGA) with zero wait states,

17ns clock-to-data output synchronousburst read mode

— 4-, 8-, 16-, and continuous-word options

for burst mode

— Buffered Enhanced Factory Programming at

2.0MByte/s (typ) using 512-word buffer

— 3.0V buffered programming at 1.14 MByte/

s (Typ) using 512-word buffer

Architecture:

— Multi-Level Cell Technology: Highest

Density at Lowest Cost

— Asymmetrically-blocked architecture

— Four 32-KByte parameter blocks: top or

bottom configuration

— 128-KByte main blocks

— Blank Check to verify an erase block

Voltage and Power:

— VCC (core) voltage: 2.3 V – 3.6 V

— VCCQ (I/O) voltage: 2.3 V – 3.6 V

— Standby current: 65uA (Typ) for 256-Mbit

— Continuous synchronous read current: 21

mA (Typ)/24 mA (Max) at 52 MHz

Datasheet

1

Security:

— One-Time Programmable Registers:

—

—

—

—

—

— 64 unique factory device identifier bits

— 2112 user-programmable OTP bits

Absolute write protection: VPP = VSS

Power-transition erase/program lockout

Individual zero-latency block locking

Individual block lock-down capability

Password Access feature

Software:

— 25µs (Typ) program suspend

— 25µs (Typ) erase suspend

— Numonyx™ Flash Data Integrator optimized

— Basic Command Set and Extended Function

Interface Command Set compatible

— Common Flash Interface capable

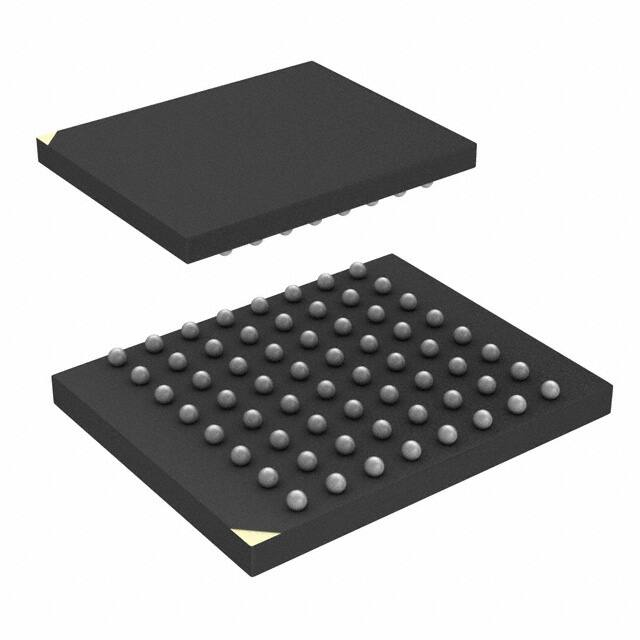

Density and Packaging

— 56-Lead TSOP package (256-Mbit only)

— 64-Ball Easy BGA package (256, 512-Mbit)

— 16-bit wide data bus

Quality and Reliability

— JESD47E Compliant

— Operating temperature: –40 °C to +85 °C

— Minimum 100,000 erase cycles per block

— 65nm ETOX™ X process technology

Jul 2011

Order Number: 320003-10

�INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH NUMONYX™ PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN NUMONYX'S TERMS AND

CONDITIONS OF SALE FOR SUCH PRODUCTS, NUMONYX ASSUMES NO LIABILITY WHATSOEVER, AND NUMONYX DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY, RELATING TO SALE AND/OR USE OF NUMONYX PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Numonyx

products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Legal Lines and Disclaimers

Numonyx may make changes to specifications and product descriptions at any time, without notice.

Numonyx, B.V. may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the

presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel

or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Numonyx reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Numonyx sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Numonyx literature may be obtained by visiting

Numonyx's website at http://www.numonyx.com.

Numonyx, the Numonyx logo, and are trademarks or registered trademarks of Numonyx, B.V. or its subsidiaries in other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2011, Numonyx, B.V., All Rights Reserved.

Datasheet

2

Jul 2011

Order Number: 320003-10

�P33-65nm

Contents

1.0

Functional Description ............................................................................................... 5

1.1

Introduction ....................................................................................................... 5

1.2

Overview ........................................................................................................... 5

1.3

Virtual Chip Enable Description.............................................................................. 6

1.4

Memory Maps ..................................................................................................... 7

2.0

Package Information ................................................................................................. 8

2.1

56-Lead TSOP..................................................................................................... 8

2.2

64-Ball Easy BGA Package .................................................................................... 9

3.0

Ballouts ................................................................................................................... 11

4.0

Signals .................................................................................................................... 13

4.1

Dual-Die Configurations ..................................................................................... 14

5.0

Bus Operations ........................................................................................................ 15

5.1

Read ............................................................................................................... 15

5.2

Write ............................................................................................................... 15

5.3

Output Disable.................................................................................................. 15

5.4

Standby ........................................................................................................... 16

5.5

Reset............................................................................................................... 16

6.0

Command Set .......................................................................................................... 17

6.1

Device Command Codes ..................................................................................... 17

6.2

Device Command Bus Cycles .............................................................................. 18

7.0

Read

7.1

7.2

7.3

7.4

8.0

Program Operation .................................................................................................. 23

8.1

Word Programming ........................................................................................... 23

8.2

Buffered Programming ....................................................................................... 23

8.3

Buffered Enhanced Factory Programming.............................................................. 24

8.4

Program Suspend .............................................................................................. 26

8.5

Program Resume............................................................................................... 27

8.6

Program Protection............................................................................................ 27

9.0

Erase Operation....................................................................................................... 28

9.1

Block Erase ...................................................................................................... 28

9.2

Blank Check ..................................................................................................... 28

9.3

Erase Suspend .................................................................................................. 29

9.4

Erase Resume................................................................................................... 29

9.5

Erase Protection ................................................................................................ 29

Operation........................................................................................................ 21

Asynchronous Page-Mode Read ........................................................................... 21

Synchronous Burst-Mode Read............................................................................ 21

Read Device Identifier........................................................................................ 22

Read CFI.......................................................................................................... 22

10.0 Security ................................................................................................................... 30

10.1 Block Locking.................................................................................................... 30

10.2 Selectable OTP Blocks ........................................................................................ 32

10.3 Password Access ............................................................................................... 32

11.0 Status Register ........................................................................................................ 33

11.1 Read Configuration Register................................................................................ 34

11.2 One-Time Programmable (OTP) Registers ............................................................. 40

12.0 Power and Reset Specifications ............................................................................... 43

Datasheet

3

Jul 2011

Order Number: 320003-10

�P33-65nm

12.1

12.2

12.3

Power-Up and Power-Down .................................................................................43

Reset Specifications ...........................................................................................43

Power Supply Decoupling....................................................................................44

13.0 Maximum Ratings and Operating Conditions ............................................................45

13.1 Absolute Maximum Ratings .................................................................................45

13.2 Operating Conditions..........................................................................................45

14.0 Electrical Specifications ...........................................................................................46

14.1 DC Current Characteristics ..................................................................................46

14.2 DC Voltage Characteristics ..................................................................................47

15.0 AC Characteristics ....................................................................................................48

15.1 AC Test Conditions.............................................................................................48

15.2 Capacitance ......................................................................................................49

15.3 AC Read Specifications .......................................................................................49

15.4 AC Write Specifications .......................................................................................54

15.5 Program and Erase Characteristics .......................................................................58

16.0 Ordering Information...............................................................................................59

16.1 Discrete Products...............................................................................................59

16.2 SCSP Products...................................................................................................60

A

Supplemental Reference Information.......................................................................61

A.1

Common Flash Interface .....................................................................................61

A.2

Flowcharts ........................................................................................................72

A.3

Write State Machine ...........................................................................................81

B

Conventions - Additional Documentation .................................................................85

B.1

Acronyms .........................................................................................................85

B.2

Definitions and Terms ........................................................................................85

C

Revision History.......................................................................................................87

Datasheet

4

Jul 2011

Order Number: 320003-10

�P33-65nm

1.0

Functional Description

1.1

Introduction

This document provides information about the Numonyx® Flash Memory (P3365nm) device and describes its features, operations, and specifications.

P33-65nm is the latest generation of Numonyx® Flash Memory (P33-65nm)

devices. P33-65nm device will be offered in 64-Mbit up through 2-Gbit densities. This

document covers specifically 256-Mbit and 512-Mbit (256M/256M) product information.

Benefits include more density in less space, high-speed interface NOR device, and

support for code and data storage. Features include high-performance synchronousburst read mode, fast asynchronous access times, low power, flexible security options,

and two industry-standard package choices.

P33-65nm is manufactured using Numonyx™ 65nm process technology.

1.2

Overview

This family of devices provides high performance at low voltage on a 16-bit data bus.

Individually erasable memory blocks are sized for optimum code and data storage.

Upon initial power-up or return from reset, the device defaults to asynchronous pagemode read. Configuring the RCR enables synchronous burst-mode reads. In

synchronous burst mode, output data is synchronized with a user-supplied clock signal.

A WAIT signal provides an easy CPU-to-flash memory synchronization.

In addition to the enhanced architecture and interface, the device incorporates

technology that enables fast factory program and erase operations. Designed for lowvoltage systems, the P33 Family Flash memory supports read operations with VCC at

3.0V, and erase and program operations with VPP at 3.0V or 9.0V. Buffered Enhanced

Factory Programming provides the fastest flash array programming performance with

VPP at 9.0V, which increases factory throughput. With VPP at 3.0V, VCC and VPP can be

tied together for a simple, ultra low power design. In addition to voltage flexibility, a

dedicated VPP connection provides complete data protection when VPP ≤ VPPLK.

The Command User Interface is the interface between the system processor and all

internal operations of the device. An internal Write State Machine automatically

executes the algorithms and timings necessary for block erase and program. A Status

Register indicates erase or program completion and any errors that may have occurred.

An industry-standard command sequence invokes program and erase automation. Each

erase operation erases one block. The Erase Suspend feature allows system software to

pause an erase cycle to read or program data in another block. Program Suspend

allows system software to pause programming to read other locations. Data is

programmed in word increments (16 bits).

The P33 Family Flash memory one-time-programmable (OTP) register allows unique

flash device identification that can be used to increase system security. The individual

Block Lock feature provides zero-latency block locking and unlocking. The P33-65nm

device adds enhanced protection via Password Access Mode which allows user to

protect write and/or read access to the defined blocks. In addition, the P33 Family

Flash memory may also provide the OTP permanent lock feature full-device to the P33130nm device.

Datasheet

5

Jul 2011

Order Number:320003-10

�P33-65nm

1.3

Virtual Chip Enable Description

The 512-Mbit P33 Family Flash memory employs a Virtual Chip Enable which combines

two 256-Mbit die with a common chip enable, CE# for Easy BGA packages. Address

A25 is then used to select between the die pair with CE# asserted, depending upon the

package option used. When chip enable is asserted and A25 is low (VIL), The lower

parameter die is selected; when chip enable is asserted and A25 is high (VIH), the

upper parameter die is selected.

Table 1:

Datasheet

6

Flash Die Virtual Chip Enable Truth Table for 512 Mbit Easy BGA Package

Die Selected

CE#

A25

Lower Param Die

L

L

Upper Param Die

L

H

Jul 2011

Order Number: 320003-10

�P33-65nm

1.4

Memory Maps

Figure 1:

P33-65nm Memory Map

A 256 Mbit

:

64- Kword Block

258

64- Kword Block

130

3 F0000 - 3FFFFF

64- Kword Block

66

020000 – 02 FFFF

64- Kword Block

5

64- Kword Block

4

010000 – 01 FFFF

00C000 – 00 FFFF

008000 – 00 BFFF

004000 – 007FFF

000000 – 003FFF

16- Kword Block

16- Kword Block

3

16- Kword Block

16- Kword Block

1

16- Kword Block

258

FF 8000 – FFBFFF

257

FF 4000 – FF7 FFF

16- Kword Block

16- Kword Block

FF 0000 – FF3 FFF

16- Kword Block

255

FE 0000 – FEFFFF

64- Kword Block

254

010000 – 01 FFFF

64- Kword Block

1

000000 – 00 FFFF

64- Kword Block

0

256

256-Mbit

7F 0000 - 7FFFFF

FFC 000 – FFFFFF

256-Mbit

FF 0000 - FFFFFF

A 256 Mbit

2

0

Bottom Boot 256 Mbit

Word Wide (x16) Mode

Top Boot 256 Mbit

Word Wide (x16 ) Mode

A 512 Mbit (256/256)

1FFC000 - 1FFFFFF

16- Kword Block

517

1FF8000 - 1FFBFFF

516

1FF4000 - 1FF7FFF

16- Kword Block

16- Kword Block

1FF0000 - 1FF3FFF

16- Kword Block

514

1FE0000 - 1FEFFFF

64- Kword Block

513

1FD0000 - 1FDFFFF

64- Kword Block

512

0020000 - 002 FFFF

64- Kword Block

5

0010000 - 001 FFFF

64- Kword Block

4

000C000 - 000FFFF

16- Kword Block

16- Kword Block

3

16- Kword Block

16- Kword Block

1

512 Mbit (256/256)

515

0008000 - 000BFFF

0004000 - 0007 FFF

0000000 - 0003 FFF

2

0

512 Mbit (256/256)

Word Wide (x16 ) Mode

Datasheet

7

Jul 2011

Order Number:320003-10

�P33-65nm

2.0

Package Information

2.1

56-Lead TSOP

Figure 2:

TSOP Mechanical Specifications (256-Mbit)

Z

A2

See Note 2

See Notes 1 and 3

Pin 1

e

See Detail B

E

Y

D1

A1

D

Seating

Plane

See Detail A

A

Detail A

Detail B

C

0

b

L

Table 2:

TSOP Package Dimensions (Sheet 1 of 2)

Millimeters

Product Information

Inches

Symbol

Note

Min

Nom

Max

Min

Nom

Max

A

-

-

1.200

-

-

0.047

Standoff

A1

0.050

-

-

0.002

-

-

Package Body Thickness

A2

0.965

0.995

1.025

0.038

0.039

0.040

Lead Width(4)

b

0.170

0.220

0.270

0.0067

0.0087

0.0106

Lead Thickness

c

0.100

0.150

0.200

0.004

0.006

0.008

Package Body Length

D1

18.200

18.400

18.600

0.717

0.724

0.732

Note

Package Body Width

E

13.800

14.000

14.200

0.543

0.551

0.559

Note

Package Height

Lead Pitch

e

-

0.500

-

-

0.0197

-

Terminal Dimension

D

19.800

20.00

20.200

0.780

0.787

0.795

Lead Tip Length

L

0.500

0.600

0.700

0.020

0.024

0.028

Datasheet

8

Jul 2011

Order Number: 320003-10

�P33-65nm

Table 2:

TSOP Package Dimensions (Sheet 2 of 2)

Millimeters

Product Information

Inches

Symbol

Note

Min

Nom

Max

Min

Nom

Max

N

-

56

-

-

56

-

Lead Tip Angle

θ

0°

3°

5°

0°

3°

5°

Seating Plane Coplanarity

Y

-

-

0.100

-

-

0.004

Lead to Package Offset

Z

0.150

0.250

0.350

0.006

0.010

0.014

Lead Count

Notes:

1.

2.

3.

4.

One dimple on package denotes Pin 1.

If two dimples, then the larger dimple denotes Pin 1.

Pin 1 will always be in the upper left corner of the package, in reference to the product mark.

For legacy lead width, 0.10mm(Min), 0.15mm(Typ) and 0.20mm(Max).

2.2

64-Ball Easy BGA Package

Figure 3:

Easy BGA Mechanical Specifications (256-Mbit, 512-Mbit)

Ball A1

Corner

D

1

E

Ball A1

Corner

2

3

4

S1

5

6

7

8

8

A

A

B

B

C

C

D

D

E

E

F

F

G

G

H

H

Top View - Ball side down

7

6

5

4

3

2

1

S2

b

e

Bottom View - Ball Side Up

A1

A2

A

Seating

Plane

Y

Note: Drawing not to scale

Datasheet

9

Jul 2011

Order Number:320003-10

�P33-65nm

Table 3:

Easy BGA Package Dimensions

Millimeters

Product Information

Inches

Symbol

Notes

Min

Nom

Max

Min

Nom

Max

A

-

-

1.200

-

-

0.0472

Ball Height

A1

0.250

-

-

0.0098

-

-

Package Body Thickness

A2

-

0.780

-

-

0.0307

-

Package Height

Ball (Lead) Width

b

0.330

0.430

0.530

0.0130

0.0169

0.0209

Package Body Width

D

9.900

10.000

10.100

0.3898

0.3937

0.3976

Note

E

12.900

13.000

13.100

0.5079

0.5118

0.5157

Note

[e]

-

1.000

-

-

0.0394

-

Package Body Length

Pitch

Ball (Lead) Count

N

-

64

-

-

64

-

Seating Plane Coplanarity

Y

-

-

0.100

-

-

0.0039

Corner to Ball A1 Distance Along D

S1

1.400

1.500

1.600

0.0551

0.0591

0.0630

Note

Corner to Ball A1 Distance Along E

S2

2.900

3.000

3.100

0.1142

0.1181

0.1220

Note

Note:

Daisy Chain Evaluation Unit information is at Numonyx™ Flash Memory Packaging Technology http://

developer.numonyx.com/design/flash/packtech.

Datasheet

10

Jul 2011

Order Number: 320003-10

�P33-65nm

3.0

Ballouts

Figure 4:

A16

A15

A14

A13

A12

A11

A10

A9

A23

A22

A21

VSS

VCC

WE#

WP#

A20

A19

A18

A8

A7

A6

A5

A4

A3

A2

A24

RFU

VSS

Notes:

1.

2.

3.

4.

56-Lead TSOP Pinout (256-Mbit)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

Numonyx®

Flash Memory (P33)

56-Lead TSOP Pinout

14 mm x 20 mm

Top View

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

WAIT

A17

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

ADV#

CLK

RST#

VPP

DQ11

DQ3

DQ10

DQ2

VCCQ

DQ9

DQ1

DQ8

DQ0

VCC

OE#

VSS

CE#

A1

A1 is the least significant address bit.

A24 is valid for 256-Mbit densities; otherwise, it is a no connect (NC).

No Internal Connection on VCC Pin 13; it may be driven or floated. For legacy designs, pin can be tied to Vcc.

One dimple on package denotes Pin 1, which will always be in the upper left corner of the package, in reference to the

product mark.

Datasheet

11

Jul 2011

Order Number:320003-10

�P33-65nm

Figure 5:

64-Ball Easy BGA Ballout (256-Mbit, 512-Mbit)

1

2

3

4

5

6

7

8

8

7

6

5

4

3

2

1

A1

A6

A8

VPP

A13

VCC

A18

A22

A22

A18

VCC

A13

VPP

A8

A6

A1

A2

VSS

A9

CE#

A14

A25

A19

RFU

RFU

A19

A25

A14

CE#

A9

VSS

A2

A3

A7

A10

A12

A15

WP#

A20

A21

A21

A20

WP#

A15

A12

A10

A7

A3

A4

A5

A11 RST# VCCQ VCCQ A16

A17

A17

A16 VCCQ VCCQ RST# A11

A5

A4

DQ1

DQ8

OE# WAIT ADV# DQ12 DQ11 DQ10 DQ0

RFU

A

A

B

B

C

C

D

D

E

E

DQ8

DQ1 DQ9

DQ3

DQ4

CLK DQ15 RFU

RFU

DQ0 DQ10 DQ11 DQ12 ADV# WAIT OE#

RFU DQ15

CLK

DQ4

DQ3

DQ9

F

F

G

G

A23

RFU

DQ2 VCCQ DQ5 DQ6

DQ14 WE#

WE# DQ14 DQ6

DQ5 VCCQ DQ2

RFU

A23

RFU

VSS

VCC

DQ7

A24

DQ13 VSS VCC

VSS

RFU

H

H

VSS

DQ13 VSS

Easy BGA

Top View- Ball side down

Notes:

1.

2.

3.

4.

A24

DQ7

VSS

Easy BGA

Bottom View- Ball side up

A1 is the least significant address bit.

A24 is valid for 256-Mbit densities and above; otherwise, it is a no connect.

A25 is valid for 512-Mbit densities; otherwise, it is a no connect.

One dimple on package denotes A1 Pin, which will always be in the upper left corner of the package, in reference to the

product mark.

Datasheet

12

Jul 2011

Order Number: 320003-10

�P33-65nm

4.0

Table 4:

Symbol

Signals

TSOP and Easy BGA Signal Descriptions (Sheet 1 of 2)

Type

Name and Function

ADDRESS INPUTS: Device address inputs. 256-Mbit: A[24:1]; 512-Mbit: A[25:1]. Note: The

virtual selection of the 256-Mbit “Top parameter” die in the dual-die 512-Mbit configuration is

accomplished by setting A25 high (VIH).

WARNING: The active address pins unused in design should not be left float. Please tie them to

VCCQ or VSS according to specific design requirements.

A[MAX:1]

Input

DQ[15:0]

Input/

Output

DATA INPUT/OUTPUTS: Inputs data and commands during write cycles; outputs data during

reads of memory, status register, OTP register, and read configuration register. Data balls float when

the CE# or OE# are deasserted. Data is internally latched during writes.

Input

ADDRESS VALID: Active low input. During synchronous read operations, addresses are latched on

the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first.

In asynchronous mode, the address is latched when ADV# going high or continuously flows through

if ADV# is held low.

WARNING: Designs not using ADV# must tie it to VSS to allow addresses to flow through.

Input

CHIP ENABLE: Active low input. CE# low selects the associated flash memory die. When asserted,

flash internal control logic, input buffers, decoders, and sense amplifiers are active. When

deasserted, the associated flash die is deselected, power is reduced to standby levels, data and

WAIT outputs are placed in high-Z state.

WARNING: All chip enables must be high when device is not in use.

CLK

Input

CLOCK: Synchronizes the device with the system’s bus frequency in synchronous-read mode.

During synchronous read operations, addresses are latched on the rising edge of ADV#, or on the

next valid CLK edge with ADV# low, whichever occurs first.

WARNING: Designs not using CLK for synchronous read mode must tie it to VCCQ or VSS.

OE#

Input

OUTPUT ENABLE: Active low input. OE# low enables the device’s output data buffers during read

cycles. OE# high places the data outputs and WAIT in High-Z.

RST#

Input

RESET: Active low input. RST# resets internal automation and inhibits write operations. This

provides data protection during power transitions. RST# high enables normal operation. Exit from

reset places the device in asynchronous read array mode.

ADV#

CE#

WAIT

Output

WAIT: Indicates data valid in synchronous array or non-array burst reads. RCR[10], (WT)

determines its polarity when asserted. WAIT’s active output is VOL or VOH when CE# and OE# are

VIL. WAIT is high-Z if CE# or OE# is VIH.

• In synchronous array or non-array read modes, WAIT indicates invalid data when asserted and

valid data when deasserted.

• In asynchronous page mode, and all write modes, WAIT is deasserted.

WE#

Input

WRITE ENABLE: Active low input. WE# controls writes to the device. Address and data are latched

on the rising edge of WE# or CE#, whichever occurs first.

Input

WRITE PROTECT: Active low input. WP# low enables the lock-down mechanism. Blocks in lockdown cannot be unlocked with the Unlock command. WP# high overrides the lock-down function

enabling blocks to be erased or programmed using software commands.

WARNING: Designs not using WP# for protection could tie it to VCCQ or VSS without additional

capacitor.

WP#

VPP

Power/

Input

ERASE AND PROGRAM POWER: A valid voltage on this pin allows erasing or programming.

Memory contents cannot be altered when VPP ≤ VPPLK. Block erase and program at invalid VPP

voltages should not be attempted.

Set VPP = VPPL for in-system program and erase operations. To accommodate resistor or diode drops

from the system supply, the VIH level of VPP can be as low as VPPL min. VPP must remain above VPPL

min to perform in-system flash modification. VPP may be 0 V during read operations.

VPPH can be applied to main blocks for 1000 cycles maximum and to parameter blocks for 2500

cycles. VPP can be connected to 9 V for a cumulative total not to exceed 80 hours. Extended use of

this pin at 9 V may reduce block cycling capability.

VCC

Power

DEVICE CORE POWER SUPPLY: Core (logic) source voltage. Writes to the flash array are inhibited

when VCC ≤ VLKO. Operations at invalid VCC voltages should not be attempted.

VCCQ

Power

OUTPUT POWER SUPPLY: Output-driver source voltage.

Datasheet

13

Jul 2011

Order Number:320003-10

�P33-65nm

Table 4:

Symbol

TSOP and Easy BGA Signal Descriptions (Sheet 2 of 2)

Type

Name and Function

VSS

Power

RFU

—

RESERVED FOR FUTURE USE: Reserved by Numonyx for future device functionality and

enhancement. These should be treated in the same way as a Don’t Use (DU) signal.

DU

—

DON’T USE: Do not connect to any other signal, or power supply; must be left floating.

NC

—

NO CONNECT: No internal connection; can be driven or floated.

4.1

Figure 6:

GROUND: Connect to system ground. Do not float any VSS connection.

Dual-Die Configurations

512-Mbit Easy BGA Block Diagram

Easy BGA 512-Mbit (Dual-Die) Configuration

CE#

WP#

Top Param Die

(256-Mbit)

OE#

VCCQ

CLK

ADV#

VSS

Bottom Param Die

(256-Mbit)

Note:

Datasheet

14

VCC

VPP

WE#

A[MAX:1]

RST#

DQ[15:0]

WAIT

Amax = VIH selects the Top parameter Die; Amax = VIL selects the Bottom Parameter

Die.

Jul 2011

Order Number: 320003-10

�P33-65nm

5.0

Bus Operations

CE# low and RST# high enable device read operations. The device internally decodes

upper address inputs to determine the accessed block. ADV# low opens the internal

address latches. OE# low activates the outputs and gates selected data onto the I/O

bus.

In asynchronous mode, the address is latched when ADV# goes high or continuously

flows through if ADV# is held low. In synchronous mode, the address is latched by the

first of either the rising ADV# edge or the next valid CLK edge with ADV# low (WE#

and RST# must be VIH; CE# must be VIL).

Bus cycles to/from the P33-65nm device conform to standard microprocessor bus

operations. Table 5, “Bus Operations Summary”summarizes the bus operations and the

logic levels that must be applied to the device control signal inputs.

Table 5:

Bus Operations Summary

Bus Operation

Read

RST#

CLK

ADV#

CE#

OE#

WE#

WAIT

DQ[15:0]

VIH

X

L

L

L

H

Deasserted

Output

Asynchronous

Synchronous

Notes

VIH

Running

L

L

L

H

Driven

Output

Write

VIH

X

L

L

H

L

High-Z

Input

Output Disable

VIH

X

X

L

H

H

High-Z

High-Z

2

Standby

VIH

X

X

H

X

X

High-Z

High-Z

2

Reset

VIL

X

X

X

X

X

High-Z

High-Z

2,3

1

Notes:

1.

Refer to the Table 7, “Command Bus Cycles” on page 19 for valid DQ[15:0] during a write

operation.

2.

X = Don’t Care (H or L).

3.

RST# must be at VSS ± 0.2 V to meet the maximum specified power-down current.

5.1

Read

To perform a read operation, RST# and WE# must be deasserted while CE# and OE#

are asserted. CE# is the device-select control. When asserted, it enables the flash

memory device. OE# is the data-output control. When asserted, the addressed flash

memory data is driven onto the I/O bus.

5.2

Write

To perform a write operation, both CE# and WE# are asserted while RST# and OE# are

deasserted. During a write operation, address and data are latched on the rising edge

of WE# or CE#, whichever occurs first. Table 7, “Command Bus Cycles” on page 19

shows the bus cycle sequence for each of the supported device commands, while

Table 6, “Command Codes and Definitions” on page 17 describes each command. See

Section 15.0, “AC Characteristics” on page 48 for signal-timing details.

Note:

Write operations with invalid VCC and/or VPP voltages can produce spurious results and

should not be attempted.

5.3

Output Disable

When OE# is deasserted, device outputs DQ[15:0] are disabled and placed in a highimpedance (High-Z) state, WAIT is also placed in High-Z.

Datasheet

15

Jul 2011

Order Number:320003-10

�P33-65nm

5.4

Standby

When CE# is deasserted the device is deselected and placed in standby, substantially

reducing power consumption. In standby, the data outputs are placed in High-Z,

independent of the level placed on OE#. Standby current, ICCS, is the average current

measured over any 5 ms time interval, 5 μs after CE# is deasserted. During standby,

average current is measured over the same time interval 5 μs after CE# is deasserted.

When the device is deselected (while CE# is deasserted) during a program or erase

operation, it continues to consume active power until the program or erase operation is

completed.

5.5

Reset

As with any automated device, it is important to assert RST# when the system is reset.

When the system comes out of reset, the system processor attempts to read from the

flash memory if it is the system boot device. If a CPU reset occurs with no flash

memory reset, improper CPU initialization may occur because the flash memory may

be providing status information rather than array data. Flash memory devices from

Numonyx allow proper CPU initialization following a system reset through the use of the

RST# input. RST# should be controlled by the same low-true reset signal that resets

the system CPU.

After initial power-up or reset, the device defaults to asynchronous Read Array mode,

and the Status Register is set to 0x80. Asserting RST# de-energizes all internal

circuits, and places the output drivers in High-Z. When RST# is asserted, the device

shuts down the operation in progress, a process which takes a minimum amount of

time to complete. When RST# has been deasserted, the device is reset to

asynchronous Read Array state.

Note:

If RST# is asserted during a program or erase operation, the operation is terminated

and the memory contents at the aborted location (for a program) or block (for an

erase) are no longer valid, because the data may have been only partially written or

erased.

When returning from a reset (RST# deasserted), a minimum wait is required before the

initial read access outputs valid data. Also, a minimum delay is required after a reset

before a write cycle can be initiated. After this wake-up interval passes, normal

operation is restored. See Section 15.0, “AC Characteristics” on page 48 for details

about signal-timing.

Datasheet

16

Jul 2011

Order Number: 320003-10

�P33-65nm

6.0

Command Set

6.1

Device Command Codes

The system Central Processing Unit provides control of all in-system read, write, and

erase operations of the device via the system bus. The on-chip WSM manages all blockerase and word-program algorithms.

Device commands are written to the CUI to control all flash memory device operations.

The CUI does not occupy an addressable memory location; it is the mechanism through

which the flash device is controlled. Table 6 shows valid device command codes and

descriptions.

Note:

Table 6:

Mode

Read

Write

Datasheet

17

For 512-Mbit (256-Mbit/256-Mbit) device, all the set-up command should be re-issued

to the device when different die is selected.

Command Codes and Definitions (Sheet 1 of 2)

Code

Device Mode

Description

0xFF

Read Array

Places the device in Read Array mode. Array data is output on DQ[15:0].

0x70

Read Status

Register

Places the device in Read Status Register mode. The device enters this mode

after a program or erase command is issued. SR data is output on DQ[7:0].

0x90

Read Device ID

or Configuration

Register

Places device in Read Device Identifier mode. Subsequent reads output

manufacturer/device codes, Configuration Register data, Block Lock status,

or OTP register data on DQ[15:0].

0x98

Read Query

Places the device in Read Query mode. Subsequent reads output Common

Flash Interface information on DQ[7:0].

0x50

Clear Status

Register

The WSM can only set SR error bits. The Clear Status Register command is

used to clear the SR error bits.

0x40

Word Program

Setup

First cycle of a 2-cycle programming command; prepares the CUI for a write

operation. On the next write cycle, the address and data are latched and the

WSM executes the programming algorithm at the addressed location. During

program operations, the device responds only to Read Status Register and

Program Suspend commands. CE# or OE# must be toggled to update the

Status Register in asynchronous read. CE# or ADV# must be toggled to

update the SR Data for synchronous Non-array reads. The Read Array

command must be issued to read array data after programming has finished.

0xE8

Buffered Program

This command loads a variable number of words up to the buffer size of 512

words onto the program buffer.

0xD0

Buffered Program

Confirm

The confirm command is Issued after the data streaming for writing into the

buffer is done. This instructs the WSM to perform the Buffered Program

algorithm, writing the data from the buffer to the flash memory array.

0x80

BEFP Setup

First cycle of a 2-cycle command; initiates the BEFP mode. The CUI then

waits for the BEFP Confirm command, 0xD0, that initiates the BEFP

algorithm. All other commands are ignored when BEFP mode begins.

0xD0

BEFP Confirm

If the previous command was BEFP Setup (0x80), the CUI latches the

address and data, and prepares the device for BEFP mode.

Jul 2011

Order Number:320003-10

�P33-65nm

Table 6:

Command Codes and Definitions (Sheet 2 of 2)

Mode

Code

Device Mode

Block Erase Setup

First cycle of a 2-cycle command; prepares the CUI for a block-erase

operation. The WSM performs the erase algorithm on the block addressed by

the Erase Confirm command. If the next command is not the Erase Confirm

(0xD0) command, the CUI sets Status Register bits SR [5,4], and places the

device in Read Status Register mode.

Block Erase Confirm

If the first command was Block Erase Setup (0x20), the CUI latches the

address and data, and the WSM erases the addressed block. During blockerase operations, the device responds only to Read Status Register and Erase

Suspend commands. CE# or OE# must be toggled to update the Status

Register in asynchronous read. CE# or ADV# must be toggled to update the

SR Data for synchronous Non-array reads.

0xB0

Program or Erase

Suspend

This command issued to any device address initiates a suspend of the

currently-executing program or block erase operation. The Status Register

indicates successful suspend operation by setting either SR.2 (program

suspended) or SR 6 (erase suspended), along with SR.7 (ready). The WSM

remains in the suspend mode regardless of control signal states (except for

RST# asserted).

0xD0

Suspend Resume

This command issued to any device address resumes the suspended program

or block-erase operation.

0x60

Block lock Setup

First cycle of a 2-cycle command; prepares the CUI for block lock

configuration changes. If the next command is not Block Lock (0x01), Block

Unlock (0xD0), or Block Lock-Down (0x2F), the CUI sets SR.5 and SR.4,

indicating a command sequence error.

0x01

Block lock

If the previous command was Block Lock Setup (0x60), the addressed block

is locked.

0xD0

Unlock Block

If the previous command was Block Lock Setup (0x60), the addressed block

is unlocked. If the addressed block is in a lock-down state, the operation has

no effect.

0x2F

Lock-Down Block

If the previous command was Block Lock Setup (0x60), the addressed block

is locked down.

0xC0

Protection program

setup

First cycle of a 2-cycle command; prepares the device for a OTP register or

Lock Register program operation. The second cycle latches the register

address and data, and starts the programming algorithm to program data the

the OTP array.

0x60

Read Configuration

Register Setup

First cycle of a 2-cycle command; prepares the CUI for device read

configuration. If the Set Read Configuration Register command (0x03) is not

the next command, the CUI sets Status Register bits SR.5 and SR.4,

indicating a command sequence error.

0x03

Read Configuration

Register

If the previous command was Read Configuration Register Setup (0x60), the

CUI latches the address and writes A[15:0]to the Read Configuration

Register. Following a Configure RCR command, subsequent read operations

access array data.

0xBC

Blank Check

First cycle of a 2-cycle command; initiates the Blank Check operation on a

main block.

0xD0

Blank Check

Confirm

Second cycle of blank check command sequence; it latches the block address

and executes blank check on the main array block.

0xEB

Extended Function

Interface command

This command is used in extended function interface. first cycle of a multiplecycle command second cycle is a Sub-Op-Code, the data written on third

cycle is one less than the word count; the allowable value on this cycle are 0

through 511. The subsequent cycles load data words into the program buffer

at a specified address until word count is achieved.

0x20

Erase

0xD0

Suspend

Protection

Configuration

blank check

other

6.2

Description

Device Command Bus Cycles

Device operations are initiated by writing specific device commands to the CUI. See

Table 7, “Command Bus Cycles” on page 19. Several commands are used to modify

array data including Word Program and Block Erase commands. Writing either

Datasheet

18

Jul 2011

Order Number: 320003-10

�P33-65nm

command to the CUI initiates a sequence of internally-timed functions that culminate in

the completion of the requested task. However, the operation can be aborted by either

asserting RST# or by issuing an appropriate suspend command.

Table 7:

Command Bus Cycles (Sheet 1 of 2)

Mode

Command

Read Array

Read

Erase

Suspend

Protection

Configuration

Datasheet

19

First Bus Cycle

Second Bus Cycle

Oper

Addr(1)

Data(2)

Oper

Addr(1)

Data(2)

1

Write

DnA

0xFF

-

-

-

Read Device

Identifier

≥2

Write

DnA

0x90

Read

DBA + IA

ID

Read CFI

≥2

Write

DnA

0x98

Read

DBA + CFI-A

CFI-D

2

Write

DnA

0x70

Read

DnA

SRD

Read Status Register

Program

Bus

Cycles

Clear Status Register

1

Write

DnA

0x50

-

-

-

Word Program

2

Write

WA

0x40

Write

WA

WD

Buffered Program(3)

>2

Write

WA

0xE8

Write

WA

N-1

Buffered Enhanced

Factory Program

(BEFP)(4)

>2

Write

WA

0x80

Write

WA

0xD0

Block Erase

2

Write

BA

0x20

Write

BA

0xD0

Program/Erase

Suspend

1

Write

DnA

0xB0

-

-

-

Program/Erase

Resume

1

Write

DnA

0xD0

-

-

-

Lock Block

2

Write

BA

0x60

Write

BA

0x01

Unlock Block

2

Write

BA

0x60

Write

BA

0xD0

Lock-down Block

2

Write

BA

0x60

Write

BA

0x2F

Program OTP register

2

Write

PRA

0xC0

Write

OTP-RA

OTP-D

Program Lock

Register

2

Write

LRA

0xC0

Write

LRA

LRD

Program Read

Configuration

Register

2

Write

RCD

0x60

Write

RCD

0x03

Jul 2011

Order Number:320003-10

�P33-65nm

Table 7:

Mode

Command Bus Cycles (Sheet 2 of 2)

Command

Blank Check

Others

Extended Function

Interface

command(5)

Bus

Cycles

First Bus Cycle

Second Bus Cycle

Oper

Addr(1)

Data(2)

Oper

Addr(1)

Data(2)

2

Write

BA

0xBC

Write

BA

D0

>2

Write

WA

0xEB

Write

WA

Sub-Op

code

Notes:

1.

First command cycle address should be the same as the operation’s target address.

DBA = Device Base Address (NOTE: needed for dual-die 512Mbit device)

DnA = Address within the device.

IA = Identification code address offset.

CFI-A = Read CFI address offset.

WA = Word address of memory location to be written.

BA = Address within the block.

OTP-RA = OTP register address.

LRA = Lock Register address.

RCD = Read Configuration Register data on A[16:1].

2.

ID = Identifier data.

CFI-D = CFI data on DQ[15:0].

SRD = Status Register data.

WD = Word data.

N = Word count of data to be loaded into the write buffer.

OTP-D = OTP register data.

LRD = Lock Register data.

3.

The second cycle of the Buffered Program Command is the word count of the data to be loaded into the write buffer. This

is followed by up to 512 words of data.Then the confirm command (0xD0) is issued, triggering the array programming

operation.

4.

The confirm command (0xD0) is followed by the buffer data.

5.

The second cycle is a Sub-Op-Code, the data written on third cycle is N-1; 1=< N